1. 實驗要求及目的:

前面三個實驗我們都只用到了LED,也就是輸出。但是我們做的東西多半都是需要人機交互的,所以不能光是有輸出,還應該有輸入(其實前面也用到了輸入,那就是時鐘)。這個實驗我們會用到按鈕,通過按鈕輸入,判斷邏輯,然後利用LED來顯示出來邏輯輸出結果。

這個實驗主要是體會一下輸入的用法,難度比較小。主要實現的是C=A •B這個功能。

使用軟體:Quartus II 5.0。

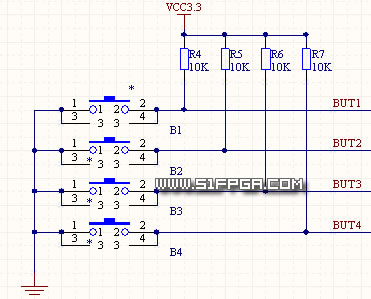

2. 硬體原理圖:

LED燈的原理圖可以參考前面實驗的圖,就不再貼了。

我們這個實驗用到兩個按鈕,BUT1和BUT2,分別對應實驗板(REV.B)的78和77引腳。按鈕平時的狀態應該是高“1”,按下之後FPGA的引腳輸入變成低“0”。輸出為LED1,引腳為實驗板(REV.B)的79引腳。

3. 程序設計

(1)設計分析:

(2)源程序 exp4.v

程序代碼:

// Base logic exp

// Designed By Smokingfish @ www.51FPGA.com zhiyuh@163.com

module exp4(led,a,b);

input a,b;

output led;

assign led=a&b;

endmodule

程序簡單明了,不用我多講什麼吧,大家都應該明白是什麼意思。這實際就是一個與門,如果有一個輸入為0,那麼輸出就為0,這樣就點亮了LED。

4. 實驗步驟

(1)打開Quartus II軟體,進入集成開發環境,點擊File->New project wizard..新建工程項目exp4,直接點擊Finish。

(2)點擊File->New..在該項目下新建Verilog HDL源程序文件exp4.v,輸入上面的源程序代碼並保存。

(3)選擇所用的FPGA器件----EP1C3T144C8,以及進行一些配置。

選擇配置器件,如果要下載程序到EPCS1的話。

選擇不需要使用的IO功能。選擇As inputs,tri-stated。

點擊兩次ok,回到主界面。

(4)為工程項目鎖定引腳:利用以下TCL文件為工程鎖定引腳。

程序代碼:

#Pin_Setup.tcl

# Setup pin setting

set_global_assignment -name RESERVE_ALL_UNUSED_PINS "AS INPUT TRI-STATED"

set_global_assignment -name ENABLE_INIT_DONE_OUTPUT ON

set_location_assignment PIN_79 -to led

set_location_assignment PIN_78 -to a

set_location_assignment PIN_77 -to b

(5)編譯工程項目:點擊Processing->Start Compilation。

(6)模擬: 自己建立模擬文件檢查自己的設計是否正確。

(7)下載目標文件到板子上:點擊Tools->Programmer,選中Jtag模式,並且選中目標文件,然後點Start。

第四個實驗結束了,很快吧,學到什麼沒有呢?不要說沒有哦。

你也可以試著做一些其他的實驗,比如非門,或門,38解碼器等等,自己設計出來比跟著別人做更有意思的。

這個實驗就不貼錄像了,我只有兩個手,不好拍。效果就是按下BUTTON1或者BUTTON2都能點亮LED1。

[admin via 研發互助社區 ] FPGA/CPLD實驗教程四(基本的邏輯門實驗)已經有5535次圍觀

http://cocdig.com/docs/show-post-43360.html