摘 要:介紹了一種利用USB2.0介面晶元ISP1581並配合FPGA晶元EP1K30TI144和DSP晶元TMS320F206實現無線數傳接收設備中數據接收存儲的方法。這種方法具有介面簡單、使用方便等特點。

數據接收存儲技術是信號採集處理領域內的一個重要課題。利用這種技術,可以把信號的實時採集和精確處理在時間上分為兩個階段,有利於獲得令人更滿意的處理結果。在無線數傳接收設備中應用數據接收存儲方法時,除了要滿足數據傳輸速率和差錯控制方面的要求外,還需要考慮如何使設備易於攜帶、介面簡單、使用方便。

傳統外設介面技術不但數據傳輸速率較低,獨佔中斷、I/O地址、DMA通道等計算機系統關鍵資源,容易造成資源衝突問題,而且使用時繁雜的安裝配置手續也給終端用戶帶來了諸多不便。近年來,USB介面技術迅速發展,新型計算機紛紛對其提供支持。USB2.0是USB技術發展的最新成果,利用USB2.0介面技術開發計算機外設,不但可以借用其差錯控制機制[1][6]減輕開發人員的負擔、獲得高速數據傳輸能力(480Mb/s),而且可以實現便捷的機箱外即插即用特性,方便終端用戶的使用。

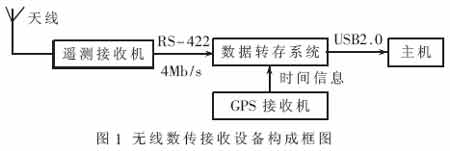

1 無線數傳接收設備總體構成

無線數傳接收設備是某靶場測量系統的一個重要組成部分。如圖1所示,該設備由遙測接收機、GPS接收機和數據轉存系統構成。遙測接收機利用天線接收經過調製的無線電波信號,解調后形成傳輸速率為4Mb/s 的RS-422電平差分串列數據流。以幀同步字打頭的有效數據幀周期性地出現在這些串列數據中。數據轉存系統從中提取出有效的數據幀,並在幀同步字后插入利用GPS接收機生成的本地時間信息,用於記錄該幀數據被接收到的時間,然後送給主機硬碟保存。

在無線數傳接收設備中,數據轉存系統是實現數據接收存儲的關鍵子系統。下面將詳細介紹該系統的硬體實現及工作過程。

2 數據轉存系統基本構成及硬體實現

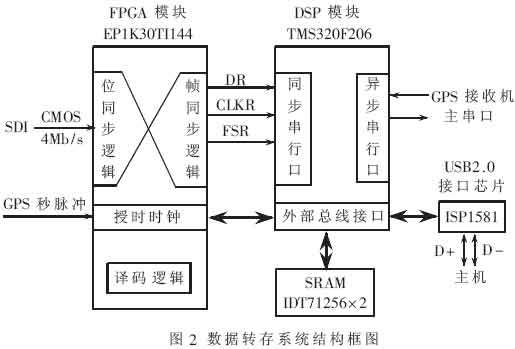

數據轉存系統主要由FPGA模塊、DSP模塊、USB2.0介面晶元構成,各個模塊之間的相互關係如圖2所示示。圖中,4Mb/s的串列數據輸入信號 SDI已由RS-422差分電平轉換為CMOS電平。為突出重點,不太重要的信號連線未在圖中繪出。下面分別介紹這幾個模塊的主要功能。

2.1 FPGA模塊實現及其功能

FPGA模塊在Altera公司ACEX系列的EP1K30TI144-2晶元中實現。其中主要的功能子模塊有:位同步邏輯、幀同步邏輯、授時時鐘和解碼邏輯。位同步邏輯主要由數字鎖相環構成,用於從串列數據輸入信號SDI中恢復出位時鐘信號。幀同步邏輯從位同步邏輯的輸出信號提取幀同步脈衝。兩者為 DSP利用其同步串列口接收串列數據作好準備。這樣,利用一對差分信號線就可以接收同步串列數據,簡化了印製電路板的外部介面。授時時鐘在DSP和GPS 接收機的協助下生成精度為0.1ms的授時信息。解碼邏輯用於實現系統互聯。

2.2 DSP模塊實現及其功能

DSP模塊是數據轉存系統的主控模塊,在TI公司16位定點DSP晶元TMS320F206[4]中實現。在DSP的外部數據空間還配置了32K×16的高速SRAM,可以緩存80餘幀數據,用於提高系統的差錯控制能力。DSP利用同步串列口接收FPGA送來的同步串列數據,利用非同步串列口接收GPS接收機送來時間信息(用於初始化FPGA授時時鐘),利用外部匯流排介面訪問FPGA授時時鐘、外部SRAM、ISP1581的片內寄存器。可以看出DSP模塊主要用於完成數據幀的接收、重組以及轉存調度等任務。

2.3 USB2.0介面晶元ISP1581

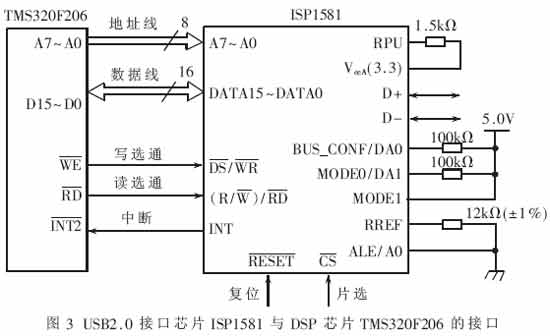

ISP1581晶元是PHILIPS公司推出的高速USB2.0設備控制器,實現了USB2.0/1.1物理層、協議層,完全符合USB2.0規範,既支持高速(480Mb/s)操作,又支持全速(12Mb/s)操作。ISP1581沒有內嵌微處理器,但對微處理器提供了靈活的介面。在上電時,通過配置 BUS_CONF/DA0、MODE1、MODE0/DA1引腳電平可以適應絕大多數的微處理器介面類型。例如,通過BUS_CONF/DA0引腳,匯流排配置可以選擇普通處理器模式(Generic Processor mode)或分割匯流排模式(Split Bus Mode);在普通處理器模式下,通過MODE0/DA1引腳可以選擇讀寫選通為8051風格或者Motorola風格。

在數據轉存系統中,ISP1581用於處理主機的高速數據傳輸。它工作在普通處理器介面模式下,採用8051風格的讀寫選通信號,由DSP晶元TMS320F206控制。兩者在選定工作方式下的信號連線如圖3所示,圖中未畫出的信號引腳可以懸空,供電引腳的連接方式在參考資料[2]第46頁有簡明描述。在FPGA解碼邏輯的作用下,ISP1581的片內寄存器被映射在DSP的片外數據空間中。DSP通過8位地址線選擇要訪問的寄存器,在讀寫選通信號的控制下,利用16 位數據線與選定的寄存器交換數據。在訪問ISP1581單位元組寄存器時,數據匯流排高位元組內容無關緊要。ISP1581通過中斷引腳INT向DSP報告發生的匯流排事件,利用D+、D-引腳完成與主機的數據交換。

3 數據轉存系統的工作過程

系統加電后,當FPGA配置過程結束時,如果有串列數據輸入,位同步邏輯和幀同步邏輯便啟動同步過程。同時,DSP片內FLASH中複位中斷服務程序c_int0()[4]被立即執行,在建立好C語言的工作環境下,它會調用主函數main()。在main()中,需要安排好一系列有先後順序的初始化工作。其中,ISP1581的初始化過程比較複雜,需要考慮設備採用的供電方式(這裡為自供電[6]方式)、插接主機和系統上電的先後次序,並需要與USB匯流排枚舉[1][6]過程相結合。

在FPGA中的位同步邏輯和幀同步邏輯均進入同步狀態,且DSP主控模塊配合主機完成初始化任務后,即可啟動數據的傳輸過程。下面介紹一下ISP1581的初始化過程及DSP控制的數據幀的接收轉存流程。

3.1 ISP1581的初始化

在初始化過程中,首先需要設置影響ISP1581自身工作方式的一些寄存器,然後與主機端USB系統配合進行,應答來自主機端的設備請求。當數據轉存系統板作為USB2.0設備通過連接器連到主機USB根集線器上的一個埠時,主機便可檢測到這一連接,接著給該埠加電,檢測設備並激活該埠,向USB 設備發送複位信號。設備收到這一複位信號后,即進入預設狀態,此後就能夠通過預設通信通道響應主機端送來的設備請求。主機通過獲得描述符請求 (GET_DESCRIPTOR)獲得設備端的詳細信息,通過設置地址請求(SET_ADDRESS)設置設備地址,通過設置配置請求 (SET_CONFIGURATION)選定合適的設備配置。在設備成功響應了這些設備請求之後,就可以與主機通信了。

在響應主機請求的過程中,DSP需要配置ISP1581的端點以實現不同類型的傳輸通道。根據數據傳輸速率的要求,除了預設的控制通道外,系統中實現了一個批傳輸(bulk)[1]類型的輸入通道。這樣,ISP1581就可以像FIFO一樣方便地從數據轉存系統向主機傳輸數據,而且具有差錯控制能力,簡化了設備端軟體設計的複雜性。

3.2 數據幀的接收轉存過程

系統正常工作時,需要與主機端程序相互配合。主機端需要開發者實現的程序包括設備驅動程序和應用程序。在Windows 2000操作系統下,USB設備驅動程序為WDM模型的驅動程序,開發環境DriverStudio為WDM型驅動程序提供了框架結構,使得驅動開發變得非常容易(參見參考文獻[5]第八、九、十章)。驅動程序接收應用程序的請求,利用USB匯流排驅動程序(USBD)和主機控制器驅動程序(HCD)通過主機控制器安排USB匯流排事務,設備端則根據這些事務調度相應的數據幀的傳輸。關於主機端如何安排匯流排事務可以查閱參考文獻[1]。以下著重介紹設備端數據的調度過程。

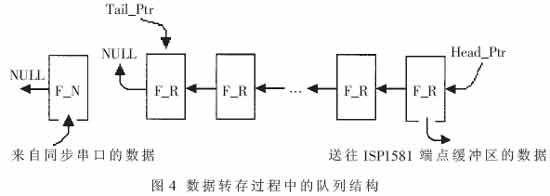

數據幀的接收轉存過程主要由DSP負責,DSP在外部SRAM中建立了一個數據幀的隊列,如圖4所示。系統主要工作在中斷驅動模式下,與同步串列口相關的中斷服務程序負責建立隊列的尾部,對應於ISP1581中斷引腳INT的中斷服務程序負責建立隊列的頭部。

當以幀同步字打頭的一幀數據以串列位流的形式到來時,FPGA產生的幀同步脈衝可以直接啟動DSP同步串列口接收數據,該同步脈衝同時以中斷方式通知 DSP為一幀數據的接收做好準備。DSP接到通知后,首先檢查外部SRAM中是否有足夠的空間容納一幀數據。如果沒有空間,則丟棄當前數據幀(根據設計, 這種情況是很少見的);如果有空間,則為當前數據幀保留足夠的空間。接著在幀起始位置填寫幀同步字,讀取授時時鐘的當前值並填寫在幀同步字后。這樣,一個新的數據幀(圖4中數據幀F_N)就建立了,但是並沒有加入到隊列中,而是要等待來自同步串列口的後繼數據嵌入該幀中后再加入到隊列中。

同步串列口的接收緩衝區在接收到若干字(由初始化時的設置決定)后,會向DSP提出中斷請求。在中斷服務程序中,DSP讀取接收緩衝區中的內容,並將其填入上述新開闢的幀F_N中。在一幀數據接收完畢后,就將該幀添加到隊列的尾部,表示該幀數據已經準備好(圖4中數據幀F_R),可以通過ISP1581送給主機硬碟保存。

DSP在查詢到隊列中有已經準備好的數據幀存在時,就設置ISP1581的端點索引寄存器(Endpoint Index Register)使其指向初始化時配置的批傳輸輸入端點,然後將隊列首幀數據通過ISP1581的數據埠寄存器(Data Port Register)填寫在端點緩衝區中。在端點緩衝區被填滿后,它就自動生效。在不能填滿端點緩衝區的情況下,可以通過設置控制功能寄存器 (Control Function Register)的VENDP位[2]強制該端點緩衝區生效。端點緩衝區生效后,在USB 匯流排上下一IN令牌到來時,該端點緩衝區中的數據就通過USB匯流排傳輸到主機中。主機成功接收到數據后,會給ISP1581以ACK應答。ISP1581 在得到ACK應答后,能夠通過INT引腳報告給DSP,DSP就可以繼續往端點中填寫該幀其餘數據。

在隊列首幀數據被成功轉移到主機后,DSP就丟棄首幀數據。如果隊列中還有數據幀,則將次首幀作為首幀,繼續前述傳輸過程;如果沒有要傳輸的數據幀,則為隊列首幀指針Head_Ptr賦空值(NULL),等待新的數據幀的到來。

USB2.0是計算機外設介面技術發展的最新成果,具有廣闊的應用前景。本文介紹了PHILIPS公司USB2.0介面晶元ISP1581在無線數傳接收設備中的應用。ISP1581晶元與FPGA晶元、DSP晶元相互配合,實現了高性能、便攜化的無線數傳接收設備。其在靶場實彈試驗中受到了用戶的好評。

[admin via 研發互助社區 ] USB2.0高速無線數傳接收設備的數據接收存儲方法已經有2039次圍觀

http://cocdig.com/docs/show-post-45159.html