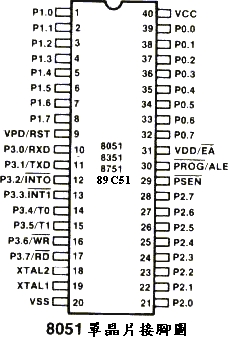

概述

Vss(20)-接地(GND)電源信號。Vcc(40)-+5V電源輸入端。8051的引腳說明用途XTAL1(19),XTAL2(18)-工作頻率輸入信號。若使用石英振蕩晶體時,則應將石英晶體的兩支引腳……

|

Vss(20)-接地(GND)電源信號。

Vcc(40)-+5V電源輸入端。

8051的引腳說明用途

XTAL1(19), XTAL2(18)-工作頻率輸入信號。若使用石英振蕩晶體時,則應將石英晶體的兩支引腳接到XTAL1與XTAL2引腳上。若使用外部的脈波信號源時波信號應接至XTALl引腳上,而XTAL2則必須接地。可使用的工作頻率範圍為:1.2 ~ l2 MHz。

RST/VST(9)-硬體重置(Reset)輸入信號。當本引腳收到一個由low上升為high的轉態信號時,8051將被重置,此時8051將其內部的特殊功能暫存器(Special Function Register, SFR)設定為預設值,並由地址0000H開始執行程序。本引腳(VPD)亦可用於8051的功率下降(Power Down)模式,當VPD維持約+5V而Vcc低於規疾的+5V+5%時,VPD將供應電源(稱之為Standby Power)給其內部的RAM使用,以保存其資料。

/EA(31)-外部存取允許(External Access Enable)輸入信號。決定程序記憶體最前面bytes(0000H-0FFFH)是來自晶元內部的ROM/EPROM (/EA=1),或來自外部的ROM/EPROM (/EA=0)。注意:由於8031晶元無內部的ROM/EPROM,故803l的/EA必須接地(即低電位信號)。

P0.0~P0.7(39~32)-介面0。本引腳有兩種用途:當作I/O口時為口0,為8位元雙向開吸極(Open Drain)的I/O口。將信號l寫入口0時,可使其引腳進入高阻貳狀態,此時可當作I/O輸入引腳。每支引腳可驅動8個LS-TTL負載。本引腳亦當作多工式的低階地址(A0-A7)及資料(DO-D7)匯流排,可供存取外部的記憶體。通常在每一個指令周期中先送出低階地址信號(此時亦伴隨著送出ALE信號),然後再送出資料信號,故這8支引腳又稱之為AD0 - AD7。

P1.0~P1.7(1~8)-介面1。為8位元雙方向性的I/O口。將信號l寫入口l時,可使其引腳由其內部提升為高電位狀態,此時可當作I/O輸入引腳。每支引腳可驅動4個LS-TTL負載。在8052系列晶元中,P1.0及P1.1可做如下之用途: T2(P1.0):計時器/計數器2外部信號輸入端。 T2EX(P1.1):計時器/計數器2在捕捉(Capture)模式時的觸發/重新載入信號輸入端。

P2.0~P2.7(21~28)-介面2。本引腳有兩種用途:當作I/O口時為8位元雙向I/O口。將信號1寫入口2時,可使其引腳由其內部提升為高電位狀態,此時可當作I/O輸入引腳。每支引腳可驅動4個LS TTL負載。本引腳亦當作高階地址(A8-A15)匯流排,以存取外部記憶體。

P3.0~P3.7(10~17)-介面3。為8位元雙方向性的I/O口。將信號1寫入口3時,可使其引腳由其內部提升為高電位狀態,此時可當作I/O輸入引腳。每支引腳可驅動4個LS-TTL負載。本引腳亦可使用於下列之用途:RXD(P3.0):串列口信號輸入端。 TXD(P3.1):串列口信號輸出端。 /INT0(P3.2):外部中斷0信號輸入端。 /INT1(P3.3):外部中斷l信號輸入端。 T0(P3.4):計時器/計數器0外部信號輸入端。 T1(P3.5):計時器/計數器l外部信號輸入端。 /WR(P3.6):外部資料記憶體寫入閃控(Strobe)信號輸出。 /RD(P3.7):外部資料記憶體讀取閃控(Strobe)信號輸出。

/PSEN(29)-程序儲存允許(Program Store ENable)閃控輸出信號。在外部程序記憶體的指令碼擷取周期時,/PSEN將送出一個閃控信號,以表示CPU正自外部的程序記憶體中讀取指令碼。

ALE(30)-地址鎖存允許(Address Latch Enable)輸出信號。當CPU自外界記憶體中擷取指令碼或存取資料時,ALE將會在一個匯流排周期(Bus Cycle)開始時送出H的信號,表示P0.0-P0.7(AD0-AD7)正送出低階地址A0-A7信號,以供外界電路鎖定這些低階地址信號。由於ALE信號頻率固定為振蕩器工作頻率的1/6,故ALE信號也可當作脈波信號源。

I/O口的結構和使用法

8051里的四個I/O都是雙向,且每個口都有鎖存器(在特殊通能暫存器里的P0至P3),輸出驅動器,和輸入緩衝器。 P0和P2的輸出驅動器,和P0的輸入緩衝器可用來存取外部記憶體的資料,在這種應用下,P0輸出外部記憶體地址的低位元組,且使用時間多工的方式作為資料的寫出與讀入口。當外部記憶體地址為16位元寬時,地址的高位元組由P2輸出。否則P2的引腳就一直輸出SFR內P2暫存器的內容。

圖中畫出了P1、P2、P3三個I/O介面里的每一隻腳的內部等效電路圖的功能圖。位元鎖存器(再SFR中的一個位元)以一個典型的D型正反器代表,再CPU送出"寫入鎖存器"的信號時,它會將內部匯流排的信號鎖住。再CPU送出"讀入鎖存器"信號時,正反器的Q輸出段的信號會放入內部匯流排而被CPU讀入。當CPU送出"讀入引腳信號時,I/O介面的引腳信號會被讀入CPU。

介面1,2和3都有內部提升電阻(不一定是電阻),介面0則為漏極開路(Open drain)輸出。而每一個I/O引腳都可以當作輸入或輸出使用(介面0和介面2當作地址/資料匯流排使用時,不能當作一般I/O使用)。當作輸入時,I/O的位元鎖存器的內容必須為"1",這個"1"會將驅動輸出的FET關掉,因此引腳(1、2和3)的信好就被內部的提升電阻至高電位,但可以由外部電路將它拉至低電位。

介面0內部則沒有上拉電阻。在PO上的輸出驅使上拉(pull-up) FET只有在外部記憶體存取時使用到,其它時間上拉用FET則處在關掉的狀態。因此PO被當成輸出時是為開泄極的型態,若寫入"1"到單元閂器時會使得兩個FET都關掉,此時引腳就呈浮接狀態。在此狀態下可將它當作高阻貳輸入使用。

|

[admin

via

研發互助社區 ]

8051的引腳說明已經有7935次圍觀

http://cocdig.com/docs/show-post-780.html