1:LVDS器件簡介

對於高速電路,尤其是高速數據匯流排,常用的器件一般有:ECL、BTL、GTL和GTL+等。這些器件的工藝成熟,應用也較為廣泛,但都存在一個共同的弱點,即功耗大,此外,採用單端信號的BTL和GTL器件,電磁輻射也較強。現在,NS公司率先推出的CMOS工藝的低電壓差分信號器件(即Low Voltage Differencial Signal 簡稱LVDS )給了我們另一種選擇。

LVDS器件是近年來National Semiconductor公司發展的一種高速傳輸晶元,它的傳輸機制是把TTL邏輯電平轉換成低電壓差分信號,以便於高速傳輸。與傳統的ECL邏輯相比,它採用CMOS工藝,它的電壓擺幅更低,只有400mv,ECL為800mv,動態功耗更小,(輸出電流3-5mA)只有ECL電路的1/7(相同的數據傳輸量),低EMI,價格更低,因而具有很大的優勢,從97-98年首先在歐洲開始得到應用。目前,NS公司的LVDS器件有以下幾個系列:

LVDS器件的推出時間不長,目前,已經在歐美地區開始應用,據了解,國內目前尚沒有應用,但已有幾家公司在進行測試和試用。現有的LVDS器件單對差分線所能傳輸的最大速率為400-600M左右,據悉NS公司正在開發速率為1G的晶元組。其它公司,如TI、朗訊,都有各自的LVDS類型的晶元。3M公司則開發了LVDS信號專用的雙絞電纜和接插件。LVDS器件主要用途為:電纜或PCB傳輸(點對點)、匯流排傳輸(BLVDS)、平板顯示器(FPD)等,傳輸速率在400M-600M,今後的LVDS器件的速度將會提高到1G,速度越來越快,品種也會越來越多。

據目前掌握的資料,未來幾年,NS將推出單對差分線傳輸速率達千兆位的LVDS收發器、低延遲的LVDS時鐘信號緩衝器/驅動器,以及36X36LVDS信號的SWITCH晶元。另外,Ericsson 和Sony 公司已經推出傳輸速率超過1G的GLVDS器件。

2:LVDS器件的標準

2.1:ANSI/TIA/EIA-644

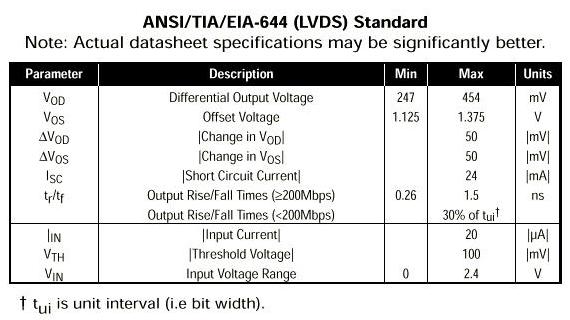

ANSI/TIA/EIA-644是由TR30.2制定的,這個標準定義了收發器的輸入輸出阻抗,但是這僅僅是一個電氣特性標準。其並不包括功能性和協議規格,完全是應用獨立的。ANSI/TIA/EIA-644打算通過使用別的協議來完善 整個介面功能。這使的這個標準在很多方面便於實現。在標準中推薦的最大操作速率是655Mbps,理論最大使用速率是1.923Gbps。傳輸速率與使用的介質損耗有關。這個標準同時也說明了最低的介質要求、收端的fail-safe電路、多路操作等。標準見下表:

表1:ANSI/TIA的LVDS標準

2.2:IEEE 1596.3 SCI-LVDS

SCI-LVDS被定義作為SCI的一個子集,在IEEE 1596.3中有詳細說明。SCI-LVDS說明了應用於高速/低功耗物理介面的電氣規範,同時也定義了用於SCI數據傳輸的包交換的編碼格式。SCI-LVDS在特定的條件下也支持高速的RAMLINK傳輸。SCI-LVDS同TIA除了在一些電氣要求和負載條件有差別,在別的方面十分相似。兩個標準支持相似的驅動輸出電平,接收門限電平,數據傳輸速率。在兩個標準中TIA的應用更為普遍,同時TIA也支持多負載情況。

3:LVDS器件的工作原理

LVDS器件的工作原理如下圖所示:

其中發送端是一個約為3.5mA的電流源,產生的3.5mA的電流通過差分線的其中一路到接收端。接收端對於直流表現為高阻,電流通過接收端的100歐姆的匹配電阻產生350mA的電壓,同時電流經過差分線的另一條流回發送端。當發送端進行狀態變化是它通過改變流經電阻的電流的方向產生有效的’0’和’1’態。

4:LVDS的特點

LVDS的特點是電流驅動模式,低電壓擺幅350mV可以提供更高的信號傳輸速率,使用差分傳輸的方式可以使信號的雜訊和EMI都減少:

A、低的輸出電壓擺幅(350mV)

B、低的信號邊緣變化率, dV/dt 0.350V/0.5ns = 0.7V/ns

C、差分特徵是磁干擾相互抵銷。

D、軟的輸出切換

E、最小的Icc切換電流變化。

同時由於使用電流驅動模式,對LVDS電路的匹配方式極為簡單,可以有以下兩種方式

圖3:LVDS介面信號的匹配圖

其中第一種方式最為簡單,也最為實用。對第二種匹配方式對共模干擾有更好的抑制作用,但是因為差分信號本身的特點一般是沒有必要的,這種匹配方式對PCB設計是的布線的難度加大,這對於高密度的PCB板的設計是不利的。對於LVDS的接收端一般可以忍受大範圍的共模對地偏壓。一般LVDS收端可以忍受+/-1V的在發端地和收端地之間的地漂移。LVDS的典型的驅動偏置是1.2V,加上可以承受的地漂移收端的偏置可以從0.2V到2.2V。推薦的收端輸入電壓範圍是從地到2.4V。參見下圖:

圖4:LVDS的邏輯電平圖

5:LVDS的設計

5.1:LVDS在PCB上的應用

LVDS在PCB的應用應該注意遵循以下準則:

5.2:LVDS在電纜中的使用

LVDS在電纜中的使用同在PCB中的使用方式並無大的差別,需要注意在不同電纜中LVDS差分信號需要不同的排布方式。

Ribbon Cable 不適合用作LVDS傳輸的介質,如果要使用應該保證地線同信號線間隔,電纜的長度儘可能短,信號的速率要儘可能低。屏蔽雙絞線比較適合作為LVDS傳輸的介質,CAT3電纜可以傳輸5m,CAT5電纜可以傳輸更遠距離的LVDS信號。

5.3:LVDS在接插件中的信號分佈和應用

LVDS在接插件的信號的分佈布不同造成的串擾的差別是很大的。但是有一點必須保證的是對於差分信號線的周圍都必須有地針,也就是說對不同的信號線是不允許相鄰排布的。下面的LVDS信號的排布可以說是一種比較好的排布方式,不但滿足了上述的基本要求,同時接插件的利益率也很高。具體可參考下圖對於實際的系統中應該使用怎樣的信號排布,要遵循的主要原則是:

6:LVDS信號的測試

LVDS信號的測試應該使用寬頻數字採樣示波器和寬頻高阻抗探頭。

1,選擇示波器的要求

首先,示波器的帶寬應該滿足被測試信號的帶寬要求。LVDS信號的模擬帶寬取決於信號的邊沿時間,不等於信號的比特速率,一般都比信號的比特速率高的多。如622Mbps的信號的帶寬可能高達1GHz。因此,選擇示波器時需要注意信號的帶寬要求。

2,探頭的選擇

由於LVDS信號是差分信號,因此,應該盡量採用差分探頭,如TEK公司的P6247等。如果沒有差分探頭,可以考慮使用兩個單端探頭,如TEK公司的P6245等。對於在線測試,要求示波器的探頭為高阻輸入。並且,由於LVDS信號的速率一般比較高,示波器探頭的寄生電容也應當選擇比較低的型號。此外,還可以把示波器作為LVDS信號的負載的形式來測試。一般採用一對50歐姆同軸電纜把信號引入到示波器的輸入端,同時,斷開板上原有的負載。 在這種情況下,要求示波器要有50歐姆輸入。同軸電纜的帶寬一般都可以達到要求,不需要考慮帶寬的影響。

3,測試方式

LVDS信號屬於高速數字信號,可以採用眼圖測試的方式來觀察信號的質量。

7:LVDS器件應用舉例

下面以DS90CR217/218為例對LVDS的器件應用加以說明。

圖5: DS90CR217/218器件的原理圖

時序要求:該晶元組內部有PLL,用於在發送端產生髮送時鐘,以及在接收端恢復時鐘。在LVDS高速碼流中,每一比特位的寬度為發送時鐘周期的1/7。如果發送時鐘為85M,周期就是11.76ns,那麼,LVDS碼流的比特位寬為1.68ns 。同一差分線對中兩條線間的相位差、差分線對之間的相位差、以及時鐘的抖動都會減小LVDS信號的採樣窗口。因此,必須保證發送器的時鐘抖動儘可能小,PLL的電源腳應單獨處理,要有足夠的去藕電容(要求0.1uF 、0.01uF 、0.001uF各一個)。此外,同一晶元上的差分信號線應嚴格等長,使差分線對之間、差分線對中的兩條線間的相位差應盡量小,以便給接收端留出盡量多的採樣余量。試驗表明,在差分線的長度控制得較好的情況下,用2071ASL(jetter Max<300ps)或50ppm 的晶振是可以滿足要求的。

上電時序及三態:在VCC電源電壓到達2V之前,發送器的輸出保持三態,當powerdown高於1.5V ,VCC到達3V后10ms,數據和時鐘輸出端開始有效。任何時刻,當Powerdown 端置低,100ns 后發送器三態;1us 后,接收器三態。任意時刻,發送器掉電后,接收器的輸入/輸出時鐘將立即停止,同時,數據輸出端將保持時鐘停振時的狀態。接收器掉電時,其輸入端將由內部的一個二極體上拉到VCC。

[admin via 研發互助社區 ] LVDS器件的原理和特點已經有12321次圍觀

http://cocdig.com/docs/show-post-44692.html